| Konversi isolasi diferensial internal |  |

| Resolusi 16-bit | |

| Akurasi: 2 sudut menit | |

| Output kait tiga status | |

| Kecepatan pelacakan kontinu tinggi | |

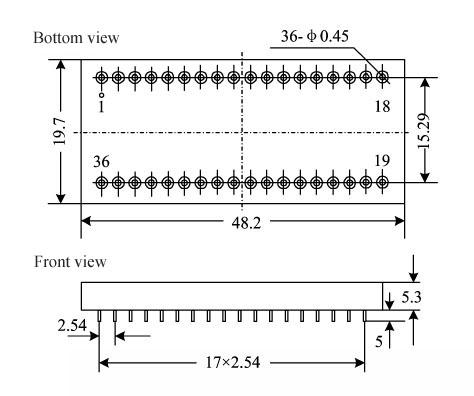

| Paket DDIP yang disegel logam 36-kawat garam-kabut-tahan | |

| Kompatibel dengan Pin-To-Pin dengan Model SDC14560 dari perusahaan DDC |

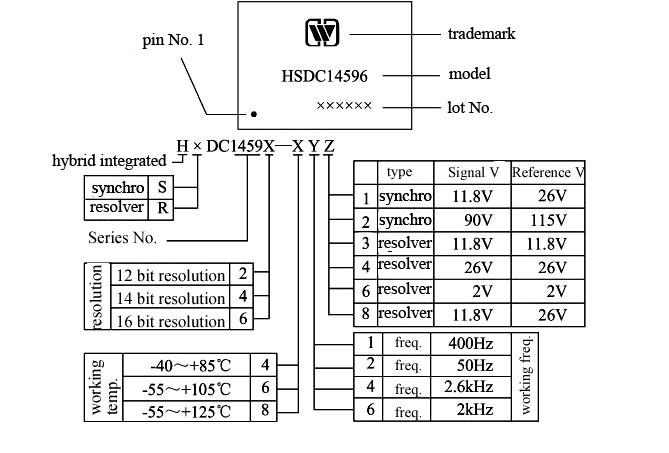

| perangkat konversi terintegrasi untuk pelacakan berkelanjutan yang dirancang di | prinsip servo model II. Produk seri ini dirancang dan |

| diproduksi oleh proses MCM, elemen inti mengadopsi chip khusus | |

| dikembangkan secara independen oleh lembaga kami. Susunan pinnya adalah | |

| kompatibel dengan produk seri SDC14560 dari perusahaan DDC Amerika, 16-bit | |

| output kait data kode biner alami paralel, DIP 36-baris sepenuhnya | |

| paket logam tertutup, memiliki keunggulan presisi tinggi, kecil | |

| volume, konsumsi daya rendah, ringan dan keandalan tinggi dll., | dan dapat digunakan secara luas dalam senjata strategis dan taktik penting seperti |

| pesawat, kapal angkatan laut, meriam, rudal, radar, tank, dll. | |

| 4. Kinerja listrik (Tabel 1, Tabel 2) | |

| Sinkronisasi ke Konverter Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1459) | |

| Tabel 1 Kondisi terukur dan kondisi pengoperasian yang direkomendasikan | |

| Maks. mutlak nilai nilai |

| Tegangan sinyal V1: nilai nilai ±20% | Referensi tegangan VRef: nilai nilai ±20% | Frekuensi operasi f: nilai nilai ±20% | |

| Suhu penyimpanan Tstg: -65~150℃ | Kondisi operasi yang direkomendasikan | ||

| Tegangan suplai logis VL: 5±0,5V | Tegangan pasokan Vs: 15± 0,75V | ||

| Tegangan sinyal V1: nilai nilai ±10% | Referensi tegangan VRef: nilai nilai ±20% | Frekuensi operasi f: nilai nilai ±20% | — |

| Rentang suhu operasi (TA): -55℃~125℃ | Catatan: * menunjukkan itu dapat disesuaikan sesuai kebutuhan pengguna. | Tabel 2 Karakteristik listrik | Parameter |

| Kondisi | — | HSDC14569 Seri | (VSu003d15V, VLu003d+5V) |

| Standar militer (Q/HW20725-2006) | — | 2V | min. |

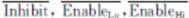

| Maks. | — | Resolusi | Kode digital sistem biner paralel |

| 16 bit | — | 2V | Ketepatan |

| ± 10% dari tegangan sinyal, tegangan referensi dan rentang fluktuasi frekuensi operasi | — | -2 menit sudut | +2 sudut menit |

| Rentang frekuensi referensi | — | 50Hz | 2600Hz |

| Rentang referensi tegangan | — | 115V | Referensi masukan impedansi |

4.4kΩ 4.4kΩ | — | 0 | 129,2 kΩ |

Rentang tegangan sinyal Rentang tegangan sinyal | — | 0 | 90V |

Impedansi masukan sinyal Impedansi masukan sinyal | — | 0 | 4.4kΩ |

| 102,2 kΩ | — | Pergeseran fase sinyal/referensi | —70 ° |

| +70 ° | — | Masukkan level logika | Logika “1” ≥3.3V |

| Logika “0” ≤0.8V | — | memasukkan | 0.8V |

| memasukkan | — | 0.8V | |

| memasukkan | — | — | 0.8V |

| Keluaran tingkat logika | — | — | Logika “1” ≥3.3V |

| Logika “0” ≤0.8V | — | — | Keluaran kode sudut digital |

| Logika “1” ≥3.3V | — | — | Logika “0” ≤0.8V |

| Mengonversi keluaran sinyal sibuk (CB) | — | 200ns | 600ns |

| Deteksi kesalahan Output bit | Logika “0” menunjukkan kesalahan | — | Memuat kapasitas |

| 3TTL | Melacak kecepatan | ||

| 2.5rps | Akselerasi konstan | ||

| +10V Saat ini VSu003d+15V 10mA |  VS u003d—15V |

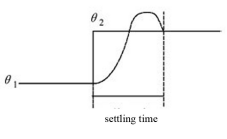

kecepatan. Proses osilasi sudut digital keluaran ditunjukkan pada

kecepatan. Proses osilasi sudut digital keluaran ditunjukkan pada 6. Prinsip operasi (Gbr. 3)

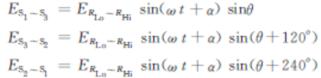

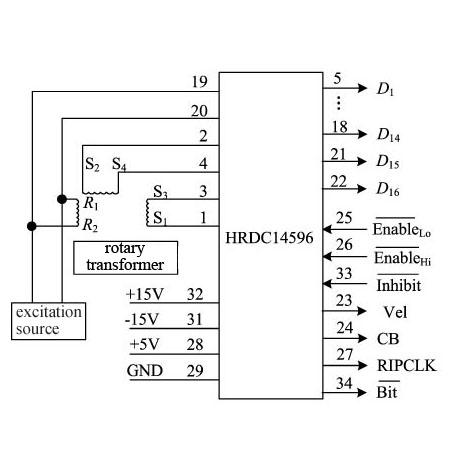

6. Prinsip operasi (Gbr. 3)| Sinkronisasi ke Konverter Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1459) Sinyal masukan sinkronisasi (atau penyelesai) diubah menjadi sinyal ortogonal melalui isolasi diferensial internal: | |

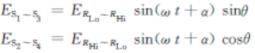

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofDi mana, θ adalah sudut masukan analog. Gbr.2 Kurva respon langkah | Kedua sinyal ini dan sudut digital dari penghitung reversibel internalof dikalikan dalam pengali fungsi Sinus dan Cosinus dan adalah kesalahan diperlakukan: |

| amplifikasi, diskriminasi fase dan filtrasi integrasi, jika | -φ≠0, osilator yang dikontrol tegangan akan mengeluarkan pulsa, dan | penghitung reversibel, hingga -φ menjadi nol dalam akurasi | konverter, selama proses ini, konversi melacak perubahan | sudut masukan sepanjang waktu. | Metode membaca: |

| 1 | S1 | Berikut dua metode yang tersedia untuk transfer data: | 25 |  | (1) Metode penghambatan: |

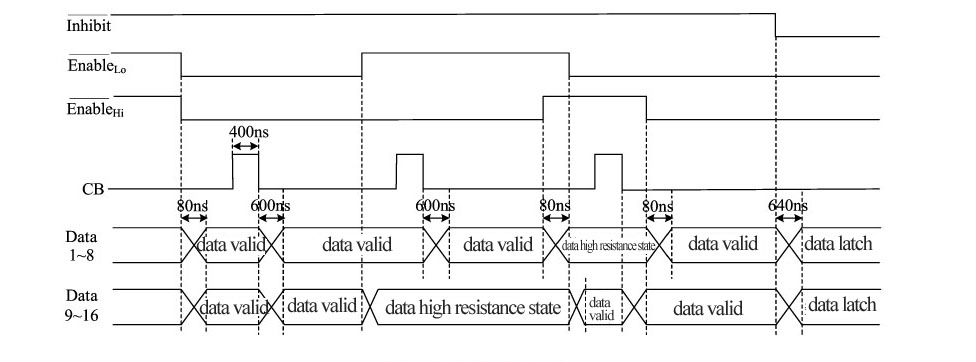

| 2 | S2 | Setelah 640n dari | 26 |  | logika rendah, data keluaran valid, dan konverter menyadari transfer data melalui |

| 3 | S3 | dan | 27 | . Setelah Inhibit dilepaskan, sistem akan secara otomatis menghasilkan pulsa dengan lebar yang sama dengan pulsa sibuk untuk pembaruan data. | (2) Mode payudara: |

| 4 | S4 | Di tepi naik denyut Sibuk, penghitung tiga-status terbalik dihitung; di tepi menurun dari pulsa Sibuk, ini secara internal menghasilkan pulsa kait dengan lebar yang sama dengan pulsa Sibuk untuk memperbarui data kait tiga keadaan, urutan waktu transfer data ditunjukkan setelah kata 6004 lainnya, pada Gambar. dengan logika Sibuk rendah, transfer data yang stabil adalah valid. Dalam mode pembacaan asinkron, output Sibuk adalah rangkaian denyut tingkat-CMOS. Lebar level tinggi dan rendahnya bergantung pada frekuensi pengoperasian dan kecepatan rotasi perangkat yang dipilih. | 28 | VL | Gbr.4 Urutan waktu transfer data |

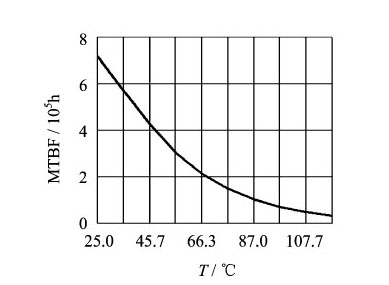

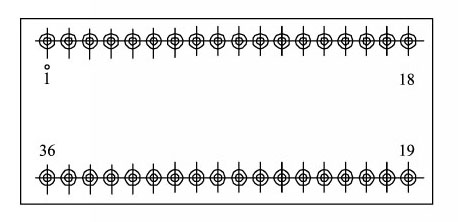

| 7. Kurva MTBF (Gbr.5) | Sinkronisasi ke Konverter Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1459) | Gbr.5 Kurva suhu MTBF | 29 | 8.Penandaan pin (Gbr.6, Tabel 3) | Sinkronisasi ke Konverter Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1459) |

| 19 | Gbr.6 Penandaan pin (Tampilan bawah) | (Catatan: menurut GJB/Z299B-98, kondisi tanah dianggap baik) | 30 | NC | Tabel 3 Penunjukan pin |

| 20 | RL | Pin | 31 | Simbol | Berarti |

| 21 | Pin | Simbol | 32 | VS | Berarti |

| 22 | Masukan penyelesai S1 (atau masukan sinkronisasi S1) | Kontrol Digital yang Diaktifkan untuk 8 bit yang lebih rendah | 33 | Masukan penyelesai S2 (atau masukan sinkronisasi S2) | Kontrol Digital yang Diaktifkan untuk 8 bit yang lebih tinggi |

| 23 | Masukan penyelesai S3 (atau masukan sinkronisasi S3) | RIPCLK | 34 | Keluaran sinyal nol bit | Masukan penyelesai S4 (biarkan tidak terhubung) |

| 24 | CB | +5V catu daya | 5月18日 | NC | D1-D14 |

| Output digital 1(MSB)-14 | GND |

| Tanah | RHi |

| Masukan sinyal referensi terakhir | Tidak ada koneksi |

| RL | Input sinyal referensi akhir rendah |

-VS

-VS -15V Sumber daya

-15V Sumber daya

H15 Keluaran digital 15

Keluaran digital 15 ).

).

+15V Sumber daya

H16

Output digital 16 (LSB)

Menghalangi

Masukan sinyal statis

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Input sinyal referensi akhir rendahofLebih rendah | Input sinyal yang diaktifkan digit 8-bit, pin ini adalah pin input logika dariofkontrol gating data, fungsinya adalah untuk melakukan kontrol tiga negara |

|  |

| eksternal pada data output 8-bit yang lebih rendah dari konverter. tingkat rendah adalah | valid, data keluaran 8-bit yang lebih rendah dari konverter menempati data |

status resistansi, dan perangkat tidak menempati bus data. Memungkinkandan waktu tunda rilis adalah 600ns (maks). | lebih tinggi | Input sinyal yang diaktifkan digit 8-bit, pin ini adalah pin input logika dari | kontrol gating data, fungsinya adalah untuk melakukan kontrol tiga negara | eksternal pada data output 8-bit yang lebih tinggi dari konverter. Level rendah | valid, data output 8-bit yang lebih tinggi dari konverter menempatibus data; Pada level tinggi, pin data keluaran 8-bit yang lebih tinggi berada di posisi tinggi | status resistansi, dan perangkat tidak menempati bus data. Memungkinkan | dan waktu tunda rilis adalah 600ns (maks). | Menghambat statis |

input sinyal, pin ini adalah pin input logika kontrol, fungsinya | adalah untuk mengeluarkan data secara eksternal ke konverter untuk mewujudkan opsional | Nilatching atau kontrol bypass. Pada tingkat tinggi, data keluaran dari | konverter langsung mengeluarkan tanpa mengunci; pada tingkat rendah, output | data konverter terkunci, data tidak diperbarui, tetapiloop internal tidak terganggu, dan pelacakan mengoperasikan semua | waktu, Inhibit telah menghubungkan tahanan pull-up secara internal. Setelah penundaan 600ns (maks) sebesar | Au tepi sinyal statis yang menurun, data menjadi stabil (apakah | perangkat menempati bus data, yaitu kapan mengeluarkan data tergantungpada keadaan | danOutput sinyal CB "Sibuk", sinyal ini menunjukkan apakah kode biner |

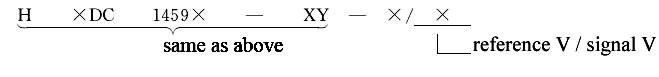

X

X