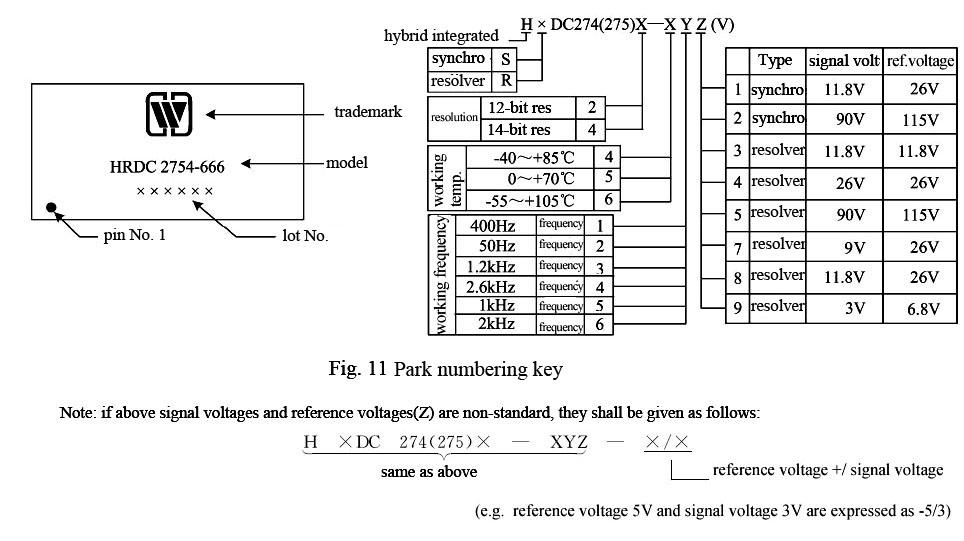

Daya operasi mengadopsi daya ±15V dan + 5V DC. Ada dua jenis sinyal keluaran: sinkronisasi tiga baris dan sinyal referensi (konverter SDC) atau penyelesai empat jalur dan sinyal referensi (konverter RDC); output mengadopsi kode digital paralel sistem biner.

| Resolusi: 12 bit, 14 bit |  |

| Kecepatan pelacakan tinggi | |

| Integrasi hibrida, kotak logam | |

| Output kait tiga status | |

| Dengan kecepatan sinyal keluaran Vel | |

| Kompatibilitas tanpa batas dengan seri AD1740 |

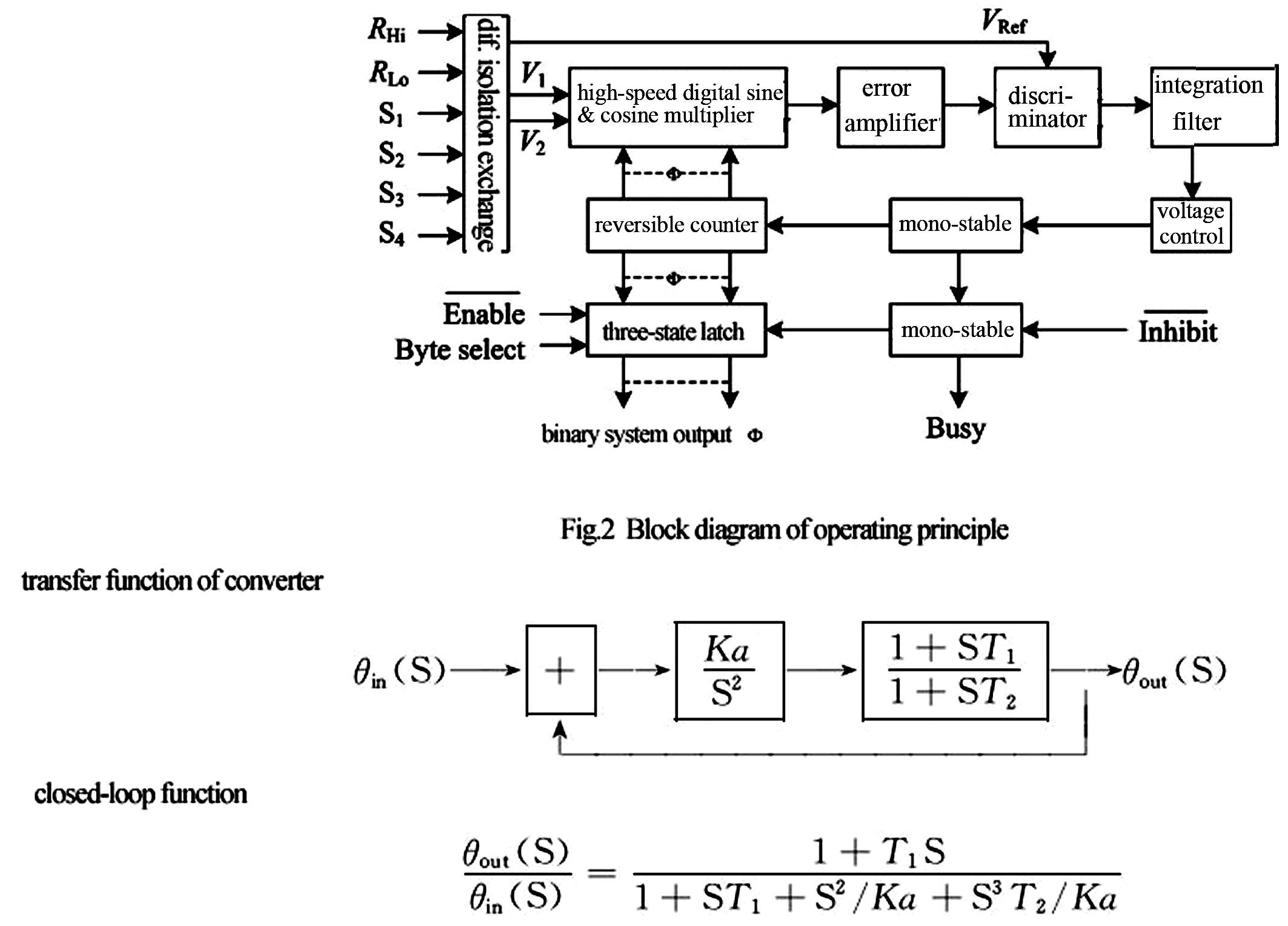

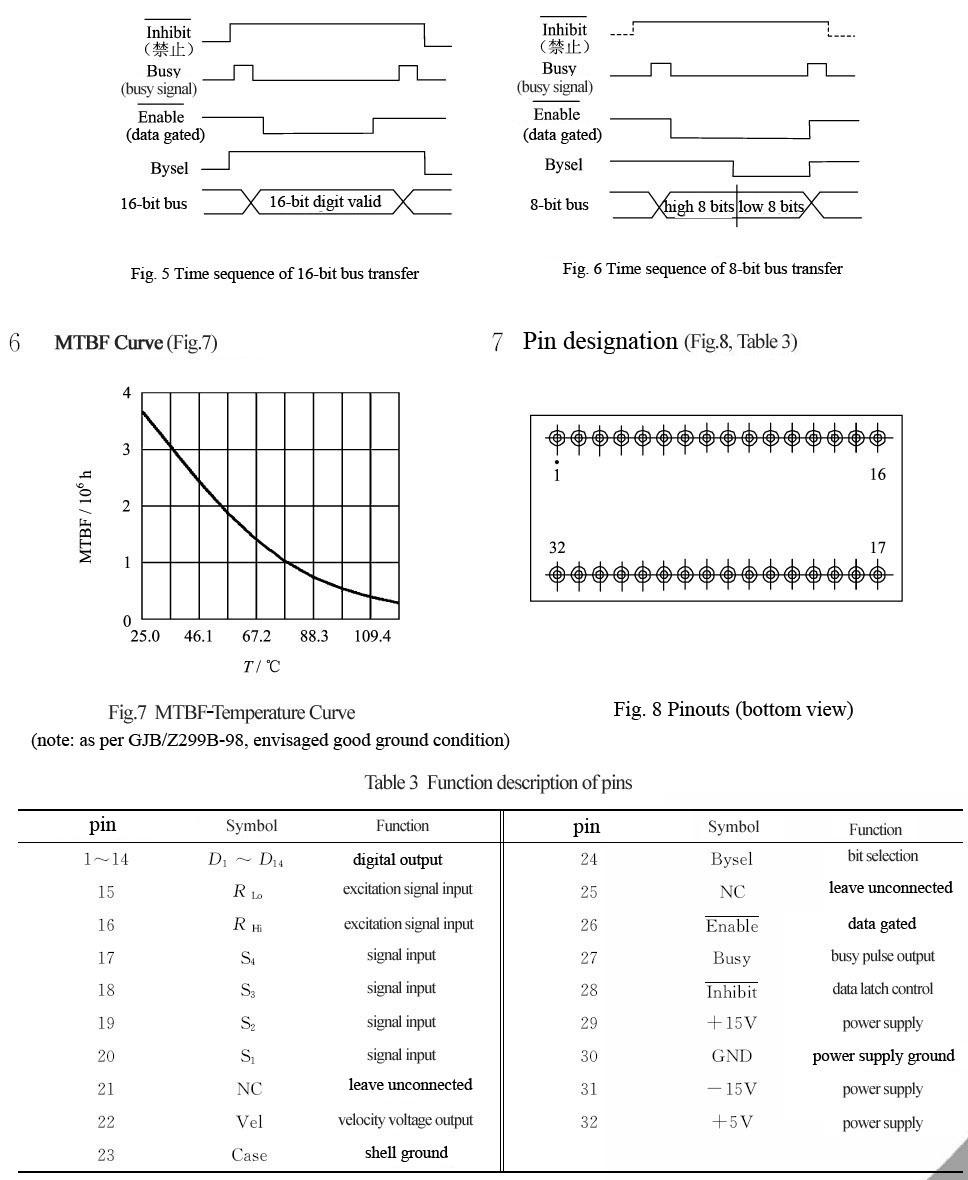

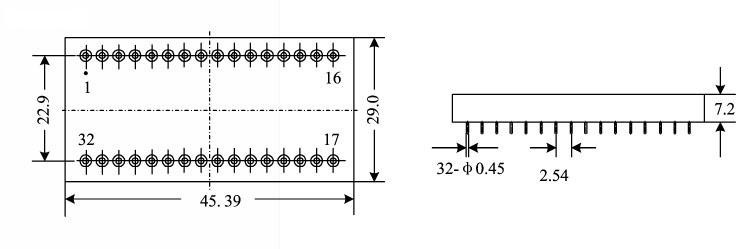

Seri HSDC/HRDC27 adalah konverter digital ke sinkronisasi atau penyelesai ke konverter digital untuk pelacakan terus menerus dari loop servo tipe II, secara paralel mengunci dan mengeluarkan data kode biner alami 12-bit atau 14-bit dengan 32-baris dual-in-line logam paket, fitur keuntungan dari volume kecil, ringan dan keandalan yang tinggi dll, itu diterapkan secara luas dalam sistem kontrol otomatis seperti sistem Radar, sistem navigasi, dll.

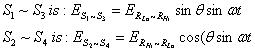

Daya operasi mengadopsi daya ±15V dan + 5V DC. Ada dua jenis sinyal keluaran: sinkronisasi tiga baris dan sinyal referensi (konverter SDC) atau penyelesai empat jalur dan sinyal referensi (konverter RDC); output mengadopsi kode digital paralel sistem biner.

Tabel 2 Kondisi yang dinilai dan kondisi operasi yang direkomendasikan

Maks. mutlak nilai nilai | Tegangan suplai Vs: ± 17.5V |

Tegangan logis VL: +5.5V | |

Kisaran suhu penyimpanan: -55℃~+125℃ | |

Kondisi operasi yang direkomendasikan | Tegangan suplai Vs: ± 5V |

Tegangan logis VL: 5V | |

Nilai efektif referensi tegangan VRef: ±10% dari nilai nominal | |

Validitas tegangan sinyal V1*: ±5% dari nilai nominal | |

Frekuensi referensi f*: 50Hz~2.6kHz | |

Rentang suhu pengoperasian TA: -40~+85℃,-55~+105℃ |

Catatan: * menunjukkan bahwa ini dapat disesuaikan sesuai kebutuhan pengguna.

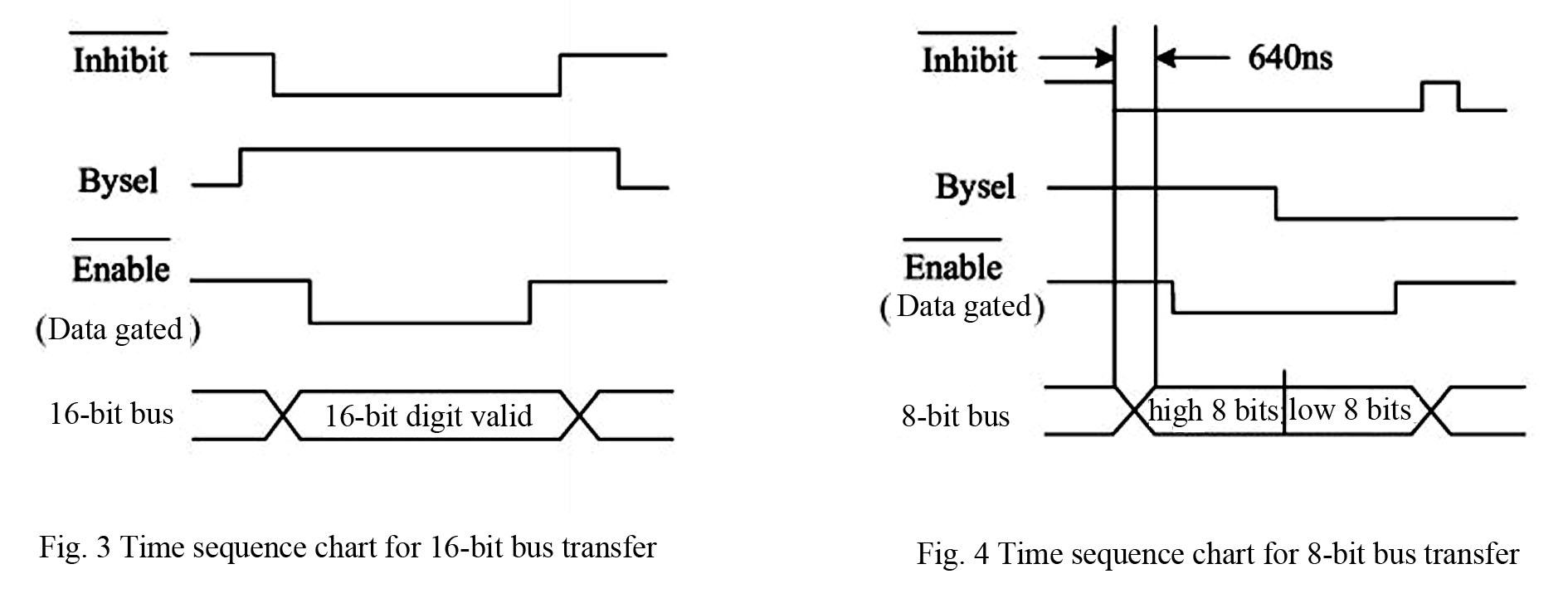

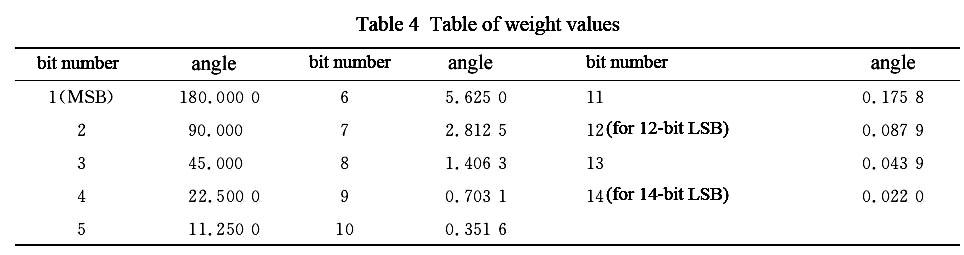

| keluaran; membaca data 12-bit atau 14-bit; atur Inhibit ke logika "1" sehingga |  |

| transfer 16-bit). | B: konverter terhubung ke bus 8-bit, bit D1~D8 terhubung ke bus data, dan sisanya kosong. |

| |

| Menghambat adalah | |

| Aktifkan untuk logika "0", data kait di dalam konverter diizinkan untuk | menjadi keluaran; jika Byse1 diatur ke logika "1", konverter langsung membaca | data 8-bit yang lebih tinggi, jika Byse1 diatur ke logika "0", konverter membaca: | bit sisanya, secara otomatis menambahkan nol untuk bit yang tidak lengkap; atur Inhibit data locking control (Inhibit signal) ke logika “1” agar siap membaca data valid berikutnya (lihat Gbr. 3 dan Gbr. 4 untuk urutan waktu transfer 8 bit) | (2) Metode sibuk (pembacaan asinkron): | Dalam mode pembacaan asinkron, Kontrol penguncian data hambat (Inhibit signal) disetel ke logika “1” atau kosong, baik loop internal selalu dalam | keadaan stabil atau apakah data keluaran valid harus ditentukan | melalui keadaan sinyal sibuk Sibuk. Saat sinyal Sibuk tinggi | level, ini menunjukkan data sedang dikonversi, dan data pada level ini |

| waktu tidak stabil dan tidak valid; ketika sinyal Sibuk berada pada level rendah, itu | menunjukkan konversi data telah selesai, dan data di ini | Au | waktu stabil dan valid. Setelah level tinggi terjadi di Sibuk selama membaca, | Au | pembacaan waktu ini tidak sah. Dalam mode membaca asinkron, Sibuk | Au | outputnya adalah rangkaian pulsa level TTL, lebar di antaranya terkait dengan | kecepatan rotasi. Demikian juga, ada juga dua penggunaan 8-bit dan 16-bit |

X

X