| Konversi isolasi diferensial internal |  |

| Resolusi: 16 bit | |

| Output kait tiga status | |

| Pelacakan tanpa gangguan selama transfer data | |

| paket logam 32-kawat |

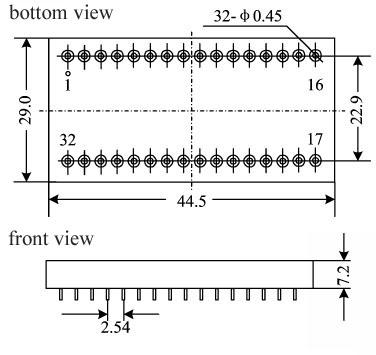

HSDC/HRDC1746 seri synchro/resolver ke konverter digital dirancang | pada prinsip prinsip pelacakan servo tipe II dan mengadopsi | |||||

input isolasi diferensial, output data mengadopsi kait tiga status | mode, sangat cocok untuk sinyal analog/sinyal digital konversi | sinkronisasi tiga-kawat dan penyelesai empat-kawat. Dengan kecepatan konversi yang cepat | dan kinerja yang stabil dan andal, perangkat ini dapat diterapkan secara luas dalam pengukuran sudut dan sistem kontrol otomatis. | Produk ini dibuat dengan proses integrasi hybrid film tebal dan | ||

Paket logam DIP 32-kawat yang benar-benar disegel. Baik desain maupun | ||||||

pembuatan produk memenuhi persyaratan GJB2438A-2002 | "Spesifikasi umum untuk sirkuit terpadu hibrid" dan spesifik | spesifikasi produk. | ||||

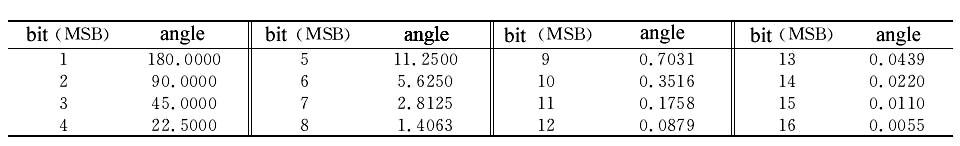

4. Kinerja listrik (Tabel 2, Tabel 3) | Konverter Sinkronisasi ke Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1746) | Tabel 2 Kondisi terukur dan kondisi pengoperasian yang direkomendasikan | Tabel 3 Karakteristik Listrik | Maks. mutlak nilai nilai | ||

Tegangan suplai Vs: ± 17.25VDC | Parameter | -3 | 3 | |||

HSDC/HRDC | Seri 1746 | 16 | ||||

Catatan | Tegangan suplai logis VL: +7V | 50 | Kisaran suhu penyimpanan: -55 ~ 150 | |||

min. | Maks. | 2 | 90 | |||

Kondisi pengoperasian yang direkomendasikan | Tegangan suplai Vs: ±15± 5% | 2 | Akurasi/menit sudut | |||

| 2.6k |  |

| Pergeseran fase antara sinyal dan eksitasi: <±10% Tegangan sinyal (nilai efektif)/V Rentang suhu operasi (TA): -40~+105℃  | |

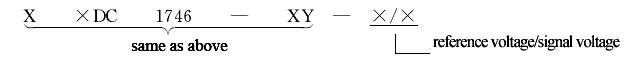

| Tegangan referensi (nilai efektif)/V | 115 |

| |

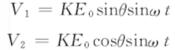

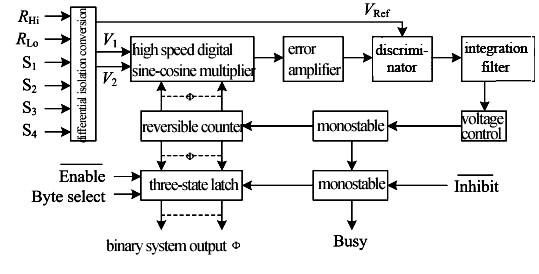

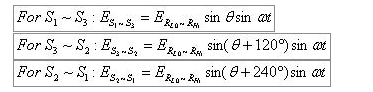

| fungsi kesalahan diperoleh: |

Melalui amplifikasi kesalahan, diskriminasi fase, dan penyaringan iniof fungsi kesalahan, sin(θ-φ) diperoleh, ketika -φu003d0 (dalam akurasi | konverter), kesalahan ini akan membuat tegangan terkontrolofpulsa koreksi keluaran osilator untuk mengubah sudut digital biner |

| |

| dari pencacah reversibel sehingga membuat nilai keluaran sama dengan | masukan dalam akurasi konverter, sistem menjadi stabil |

| dan dapat melacak perubahan sudut input . Dengan cara ini, digital biner | |

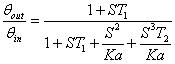

penghitung reversibel (Gbr. 2). | Gambar 2 Diagram blok sirkuit | (1) Karakteristik dinamis | Fungsi transfer konverter ditunjukkan pada Gambar. 3: | Keuntungan loop terbuka: | Fungsi loop tertutup: |

1 | NC | Untuk modul model ini Kau003d48000/S2, T1u003d7.1ms, T2u003d1.25ms | 17 | NC | Gbr. 3 Transfer fungsi konverter |

2 | D9 | (2) Metode transfer data dan urutan waktu | 18 | Kontrol pemilihan chip Aktifkan | Pin ini adalah pin input logika kontrol, fungsinya untuk output |

3 | data ke konverter untuk mewujudkan kontrol tiga keadaan. tingkat rendah adalah | valid, data keluaran konverter menempati bus data. Saat itu di | 19 | tingkat tinggi, pin keluaran data konverter ada di tiga status, the | perangkat tidak menempati bus. |

4 | Byte pilih | Pin ini adalah pin input kontrol, fungsinya untuk mengeksekusi secara eksternal | 20 | kontrol pemilihan pada data keluaran konverter dalam transfer | mode bus data 8-bit atau bus data 16-bit. Ketika transfer bus data 16-bit |

5 | mode diperlukan, jaga agar pin logika ini tetap tinggi, datanya akan | ditransfer di bus, output byte tinggi di pin D1 ke D8 (D1 adalah | 21 | bit tinggi) dan byte rendah di D9 hingga D16. Ketika transfer bus data 8-bit | mode diperlukan, data diperoleh di pin D1 hingga D8 (diurutkan dari tinggi |

6 | ke rendah), dan 8 bit tinggi dan 8 bit rendah diperoleh melalui dua waktu | urutan, dengan kata lain, ketika Byte pilih adalah logika tinggi, tinggi 8 bit | 22 | adalah output dan ketika logika rendah, output 8 bit rendah. | Kontrol penguncian data (Menghambat sinyal) Menghambat |

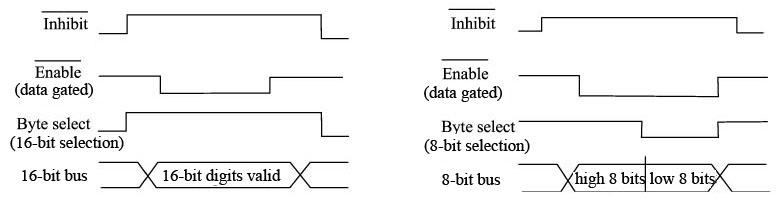

7 | Pin ini adalah pin input logika kontrol, fungsinya untuk output | data eksternal ke konverter untuk mewujudkan penguncian atau bypass opsional | 23 | kontrol. Pada tingkat tinggi, data keluaran konverter secara langsung | output tanpa latching, lihat diagram urutan waktu data |

8 | transfer. Pada level rendah, data keluaran konverter terkunci, | loop internal tidak terputus, dan pelacakan tetap berfungsi sepanjang | 24 | D1 | waktu, tetapi penghitung tidak mengeluarkan data. Saat dibutuhkan untuk mentransfer |

9 | data, konverter pertama-tama membuat sinyal kontrol Menghambat untuk mengunci data dari tinggi ke rendah, menjaga logika tetap rendah selama 640ns, kemudian mengatur Aktifkan input ke rendah (saat ini perangkat menempati bus data), dan kemudian | memperoleh data melalui Byte pilih, lalu ubah semua logika kontrol ke tinggi | 25 | D2 | untuk menyegarkan dan mengunci data agar siap untuk mentransfer |

10 | data selanjutnya, silakan lihat diagram urutan waktu transfer data Gbr.4 | dan Gbr.5. | 26 | D3 | (3) Metode redaman sinyal input (Gbr.4 dan Gbr.5) |

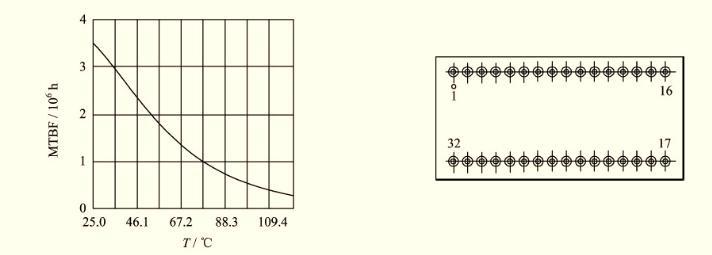

11 | Gambar 4 Urutan waktu transfer bus 16-bit | Fig5 Urutan waktu transfer bus 8-bit | 27 | D4 | 6. Kurva MTBF (Gbr. 6) |

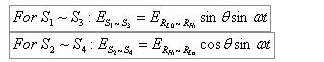

12 | Konverter Sinkronisasi ke Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1746) | 7. Penunjukan pin (Gbr.7, Tabel 4) | 28 | D5 | Konverter Sinkronisasi ke Digital atau Resolver ke Konverter Digital (Seri HSDC/HRDC1746) |

13 | S3 | Gbr.6 Kurva suhu MTBF | 29 | D6 | Gbr.7 Penunjukan pin (Tampilan bawah) |

14 | S2 | (Catatan: sesuai GJB/Z299B-98, kondisi tanah yang diharapkan baik) | 30 | D7 | Tabel 4 Deskripsi fungsional terminal timah |

15 | S1 | Pin | 31 | D7 | Simbol |

16 | NC | Berarti | 32 | NC | Pin |

Tanah | D12 | Output digital untuk 12thbit | -VS | -15V catu daya | D13 | Output digital untuk 13thbit | + VS | + catu daya 15V |

H14 | Output digital untuk 14thbit | Ni | Menghalangi | Ni | Kontrol penguncian data | H15 | Output digital untuk 15thbit |

X

X